|

|

PDF IS45S32200C1 Data sheet ( Hoja de datos )

| Número de pieza | IS45S32200C1 | |

| Descripción | SYNCHRONOUS DYNAMIC RAM | |

| Fabricantes | ISSI | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de IS45S32200C1 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

IS45S32200C1

512K Bits x 32 Bits x 4 Banks (64-MBIT)

SYNCHRONOUS DYNAMIC RAM

ISSI®

JULY 2006

FEATURES

• Clock frequency: 143 MHz

• Fully synchronous; all signals referenced to a

positive clock edge

• Internal bank for hiding row access/precharge

• Single 3.3V power supply

• LVTTL interface

• Programmable burst length:

(1, 2, 4, 8, full page)

• Programmable burst sequence:

Sequential/Interleave

• Self refresh modes

• 4096 refresh cycles every 64 ms

• Random column address every clock cycle

• Programmable CAS latency (2, 3 clocks)

• Burst read/write and burst read/single write

operations capability

• Burst termination by burst stop and precharge

command

• Automotive Temperature Grade

Option A: 0oC to +70oC

Option A1: -40oC to +85oC

• Package 400-mil 86-pin TSOP II and 90-ball BGA

• Lead free package is available

OVERVIEW

ISSI's 64Mb Synchronous DRAM IS45S32200C1 is

organized as 524,288 bits x 32-bit x 4-bank for improved

performance. The synchronous DRAMs achieve high-

speed data transfer using pipeline architecture. All inputs

and outputs signals refer to the rising edge of the clock

input.

KEY TIMING PARAMETERS

Parameter

Clk Cycle Time

CAS Latency = 3

CAS Latency = 2

Clk Frequency

CAS Latency = 3

CAS Latency = 2

Access Time from Clock

CAS Latency = 3

CAS Latency = 2

-7

7

10

143

100

5.5

8

Unit

ns

ns

Mhz

Mhz

ns

ns

Copyright © 2006 Integrated Silicon Solution, Inc. All rights reserved. ISSI reserves the right to make changes to this specification and its products at any time

without notice. ISSI assumes no liability arising out of the application or use of any information, products or services described herein. Customers are advised to

obtain the latest version of this device specification before relying on any published information and before placing orders for products.

Integrated Silicon Solution, Inc. — www.issi.com — 1-800-379-4774

Rev. B

05/18/06

1

1 page

IS45S32200C1

ISSI ®

PIN FUNCTIONS

Symbol

A0-A10

Pin No.(TSOP)

25 to 27

60 to 66

24

Type

Input Pin

BA0, BA1

CAS

CKE

22,23

18

67

Input Pin

Input Pin

Input Pin

CLK 68 Input Pin

CS 20 Input Pin

DQ0 to 2, 4, 5, 7, 8, 10,11,13

DQ31 74,76,77,79,80,82,83,85

45,47,48,50,51,53,54,56

31,33,34,36,37,39,40,42

DQM0

DQM3

16,28,59,71

DQ Pin

Input Pin

RAS 19 Input Pin

WE 17 Input Pin

VDDQ

VDD

GNDQ

GND

3,9,35,41,49,55,75,81 Supply Pin

1,15,29,43

Supply Pin

6,12,32,38,46,52,78,84 Supply Pin

44,58,72,86

Supply Pin

Function (In Detail)

Address Inputs: A0-A10 are sampled during the ACTIVE

command (row-address A0-A10) and READ/WRITE command (A0-A7

with A10 defining auto precharge) to select one location out of the memory array

in the respective bank. A10 is sampled during a PRECHARGE command to

determine if all banks are to be precharged (A10 HIGH) or bank selected by

BA0, BA1 (LOW). The address inputs also provide the op-code during a LOAD

MODE REGISTER command.

Bank Select Address: BA0 and BA1 defines which bank the ACTIVE, READ,

WRITE or PRECHARGE command is being applied.

CAS, in conjunction with the RAS and WE, forms the device command. See the

"Command Truth Table" for details on device commands.

The CKE input determines whether the CLK input is enabled. The next rising edge

of the CLK signal will be valid when is CKE HIGH and invalid when LOW. When

CKE is LOW, the device will be in either power-down mode, clock suspend mode,

or self refresh mode. CKE is an asynchronous input.

CLK is the master clock input for this device. Except for CKE, all inputs to this

device are acquired in synchronization with the rising edge of this pin.

The CS input determines whether command input is enabled within the device.

Command input is enabled when CS is LOW, and disabled with CS is HIGH. The

device remains in the previous state when CS is HIGH.

DQ0 to DQ15 are DQ pins. DQ through these pins can be controlled in byte units

using the DQM0-DQM3 pins

DQMx control thel ower and upper bytes of the DQ buffers. In read mode,

the output buffers are place in a High-Z state. During a WRITE cycle the input data is

masked. When DQMx is sampled HIGH and is an input mask signal for write accesses

and an output enable signal for read accesses. DQ0 through DQ7 are controlled by

DQM0. DQ8 throughDQ15 are controlled by DQM1. DQ16 through DQ23 are

controlled by DQM2. DQ24 through DQ31 are controlled by DQM3.

RAS, in conjunction with CAS and WE, forms the device command. See the "Command

Truth Table" item for details on device commands.

WE, in conjunction with RAS and CAS, forms the device command. See the "Command

Truth Table" item for details on device commands.

VDDQ is the output buffer power supply.

VDD is the device internal power supply.

GNDQ is the output buffer ground.

GND is the device internal ground.

Integrated Silicon Solution, Inc. — www.issi.com — 1-800-379-4774

Rev. B

05/18/06

5

5 Page

IS45S32200C1

ISSI ®

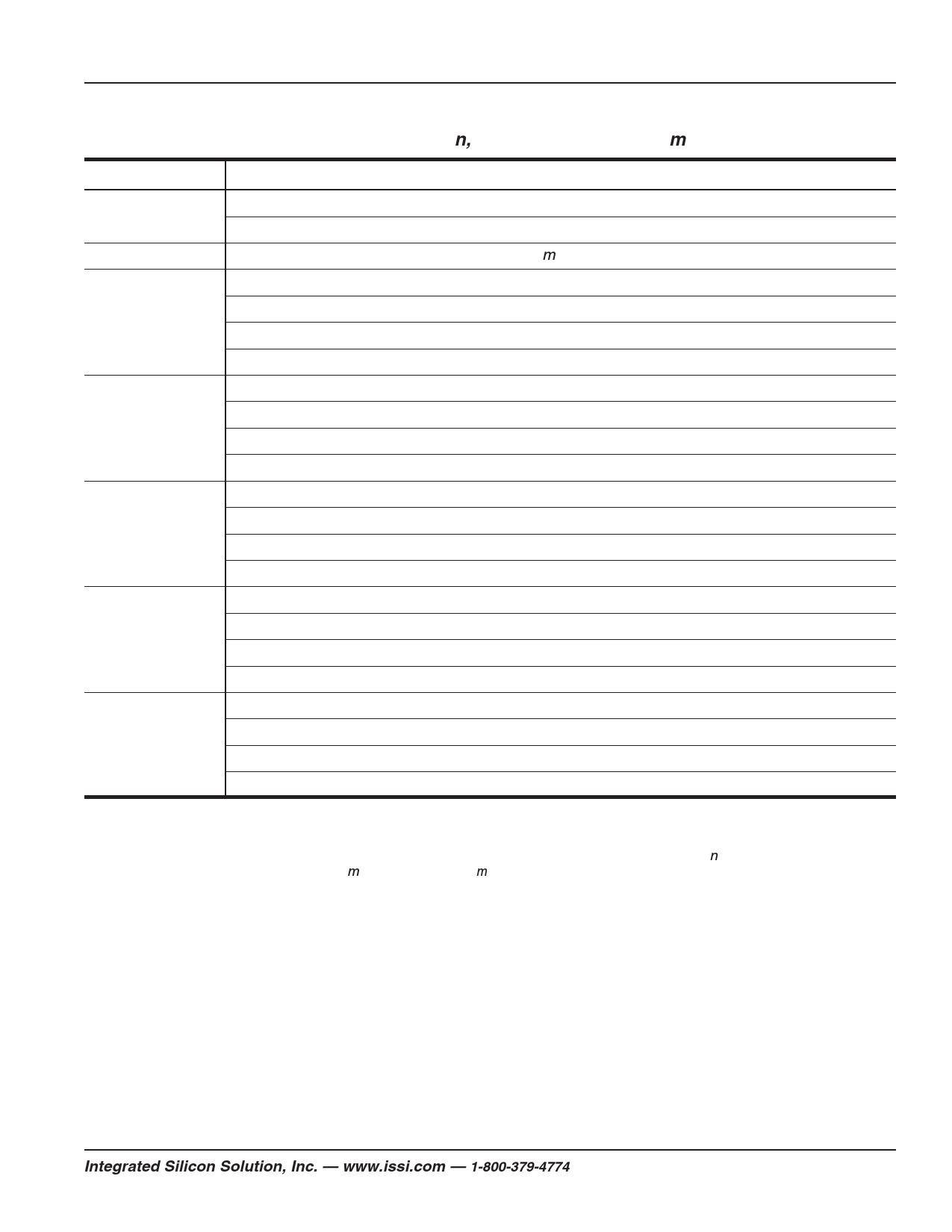

TRUTH TABLE – CURRENT STATE BANK n, COMMAND TO BANK m (1-6)

CURRENT STATE COMMAND (ACTION)

CS RAS CAS WE

Any

COMMAND INHIBIT (NOP/Continue previous operation)

HX XX

NO OPERATION (NOP/Continue previous operation)

LH HH

Idle Any Command Otherwise Allowed to Bank m

XX XX

Row ACTIVE (Select and activate row)

L L HH

Activating,

READ (Select column and start READ burst)(7)

LH LH

Active, or

WRITE (Select column and start WRITE burst)(7)

LH LL

Precharging

PRECHARGE

LL HL

Read

ACTIVE (Select and activate row)

L L HH

(Auto

READ (Select column and start new READ burst)(7,10)

LH LH

Precharge

WRITE (Select column and start WRITE burst)(7,11)

LH LL

Disabled)

PRECHARGE(9)

LL HL

Write

ACTIVE (Select and activate row)

L L HH

(Auto

READ (Select column and start READ burst)(7,12)

LH LH

Precharge

WRITE (Select column and start new WRITE burst)(7,13)

LH LL

Disabled)

PRECHARGE(9)

LL HL

Read

ACTIVE (Select and activate row)

L L HH

(With Auto

READ (Select column and start new READ burst)(7,8,14)

LH LH

Precharge)

WRITE (Select column and start WRITE burst)(7,8,15)

LH LL

PRECHARGE(9)

LL HL

Write

ACTIVE (Select and activate row)

L L HH

(With Auto

READ (Select column and start READ burst)(7,8,16)

LH LH

Precharge)

WRITE (Select column and start new WRITE burst)(7,8,17)

LH LL

PRECHARGE(9)

LL HL

NOTE:

1. This table applies when CKE n-1 was HIGH and CKE n is HIGH (Truth Table - CKE) and after tXSR has been met (if the previous

state was self refresh).

2. This table describes alternate bank operation, except where noted; i.e., the current state is for bank n and the commands shown

are those allowed to be issued to bank m (assuming that bank m is in such a state that the given command is allowable). Exceptions are

covered in the notes below.

3. Current state definitions:

Idle: The bank has been precharged, and tRP has been met.

Row Active: A row in the bank has been activated, and tRCD has been met. No data bursts/accesses and no register

accesses are in progress.

Read: A READ burst has been initiated, with auto precharge disabled, and has not yet terminated or been terminated.

Write: A WRITE burst has been initiated, with auto precharge disabled, and has not yet terminated or been terminated.

Read w/Auto

Precharge Enabled: Starts with registration of a READ command with auto precharge enabled, and ends when tRP has been met.

Once tRP is met, the bank will be in the idle state.

Write w/Auto

Precharge Enabled: Starts with registration of a WRITE command with auto precharge enabled, and ends when tRP has been

met. Once tRP is met, the bank will be in the idle state.

4. AUTO REFRESH, SELF REFRESH and LOAD MODE REGISTER commands may only be issued when all banks are idle.

5. A BURST TERMINATE command cannot be issued to another bank; it applies to the bank represented by the current state only.

6. All states and sequences not shown are illegal or reserved.

Integrated Silicon Solution, Inc. — www.issi.com — 1-800-379-4774

Rev. B

05/18/06

11

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet IS45S32200C1.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| IS45S32200C1 | SYNCHRONOUS DYNAMIC RAM | ISSI |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |